Blocco di acquisizione analogico

Lo schema del blocco di

acquisizione analogico č composto da

tre sezioni distinte. Le descrivo brevemente, in seguito dovrň organizzare

tutto in modo piů ordinato e appronfondito.

1. CPLD e memoria.

Questa č la sezione che si occupa della memorizzazione dei dati. Segue una

descrizione dei segnali della CPLD e del loro utilizzo:

- CD0...CD7 (I/O): bus

dati esterno, comune a tutti i moduli di acquisizione e al modulo

principale.

- CA0...CA1 (I): segnali

di indirizzamento esterni. Per selezionare la CPLD č necessario che sia CA0

che CA1 siano posti a "1". Questa scelta č stata fatta per

ridurre al minimo i pin della CPLD utilizzati e per rendere semplice

l'impostazione dell'indirizzo di ciascun modulo (bastano un paio di

ponticelli). Ovviamente il numero dei dispositivi indirizzabili si riduce

considerevolmente rispetto all'utilizzo di una decodifica degli indirizzi

"canonica"; considerando ad esempio otto bit, anziché 256 moduli

se ne possono indirizzare 28, che comunque č giŕ un buon numero.

In compenso questo metodo permette di indirizzare contemporaneamente piů

moduli, rendendo ad esempio possibile la configurazione simultanea con una

singola scrittura.

- RD (I): segnale di

controllo per leggere il dato memorizzato nella SRAM nella posizione attuale

(a ogni lettura l'indirizzo viene incrementato). Questa funzione deve essere

utilizzata soltanto quando l'acquisizione non č in corso

(GO="0"). Conoscendo la dimensione della SRAM e il numero di

campioni di pre- e post-trigger, č possibile posizionarsi nel punto

desiderato della SRAM.

- WR0 (I): segnale di

controllo per scrivere il valore di otto bit che sarŕ confrontato con i

valori campionati dall'ADC per verificare la condizione di trigger.

- WR1 (I): segnale di

controllo per scrivere la "configuration word" di tre bit. Il bit

0 seleziona il fronte sul quale eseguire il trigger ("0"=salita

"1"=discesa); il bit 1 č l'enable del trigger

("0"=disabilitato "1"=abilitato; ovviamente soltanto un

modulo deve avere il trigger abilitato); il bit 2 č il bit di

"sblocco" di GO (una volta che una CPLD pone GO="0",

esso non sarŕ piů rilasciato finché non verrŕ scritto un "1"

in questo bit).

- WR2 (I): segnale di

controllo per scrivere la "control word" di quattro bit. I primi

tre selezionano il guadagno di ingresso; l'ultimo bit abilita o meno il

disaccoppiamento dell'ingresso ("0"=DC "1"=AC).

- CLOCK (I): il clock

che piloterŕ l'ADC. Esso deve essere giŕ stato impostato alla frequenza

desiderata da qualche dispositivo a monte; la CPLD si limita a passarlo

inalterato all'ADC e alla SRAM.

- GO (I/O, open drain):

il segnale di sincronizzazione fra i vari moduli. Quando GO="0"

significa che un modulo ha richiesto un'interruzione del campionamento

(condizione di trigger per i moduli di acquisizione, o scadenza del timeout

per il modulo principale).

- MEMRD (O): segnale di

pilotaggio per la lettura della SRAM. Viene generato in base a CA0, CA1 e

RD.

- DATA0...DATA7 (I): bus

dati interno del blocco di acquisizione; collega ADC, SRAM e CPLD. La CPLD

si limita a "guardare" i dati mentre passano per verificare la

condizione di trigger e pilotare opportunamente i segnali di clock e di

enable.

- ADDR0...ADDR15 (O): il

bus indirizzi interno del blocco di acquisizione. Serve per indirizzare in

modo opportuno la SRAM.

- CLKOUT (O): pilota l'ADC.

Attivo soltanto quando GO="1".

- CLKOUT

(O): pilota la SRAM. La fase č invertita rispetto a CLKOUT per permettere

di far stabilizzare il dato in uscita all'ADC, per poi memorizzarlo.

- CTLOUT0...CTLOUT3 (O):

sono i bit della "control word" direttamente riproposti

all'esterno.

- TDI, TDO, TMS, TCK:

questi segnali servono per l'interfacciamento al bus JTAG (IEEE-1149.1),

necessario per la programmazione della CPLD. Ogni modulo disporrŕ di uno

zoccolo al quale si potrŕ collegare l'appropriato programmatore.

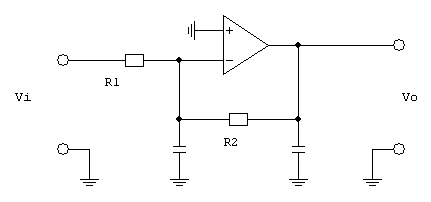

2. Stadio di ingresso.

Il frontend analogico č abbastanza "canonico". L'ingresso č adattato

per una normale sonda 10:1 (10 Mohm, compensatore 10-15 pF); dopodiché ci sono

i blocchi per eliminare le componenti in continua nel caso che sia selezionata

la modalitŕ AC. A questo punto potrebbe seguire un classico amplificatore da strumentazione con ingresso

differenziale e guadagno unitario: non tutti gli oscilloscopi dispongono di

ingressi differenziali, ma questa funzione si puň rivelare utile in parecchie

situazioni. Negli schemi ho riportato sia lo stadio di ingresso in versione

differenziale che in versione single-ended, anche se credo che nel primo

prototipo opterň per quest'ultima soluzione. In ogni caso il resto del capitolo

č riferito alla versione differenziale.

L'uscita (single ended)

dell'amplificatore da strumentazione viene amplificata/attenuata da un

operazionale in configurazione invertente; il guadagno č determinato dalla

resistenza che c'č fra i punti RGAINN e RGAINP, impostata dallo stadio di

commutazione del guadagno. Originariamente avevo tentato di impostare il

guadagno agendo direttamente sull'amplificatore di strumentazione, secondo

questo noto schema (immagine presa da Sedra-Smith, "Microelectronic

Circuits" quarta edizione, pag. 90):

Il guadagno č dato dalla

formula:

Adiff=(1+2R2/R1)*(R4/R3)

Come si vede si puň

impostare il guadagno agendo su una singola resistenza, R1. Tale

resistenza č anche quella che determina la corrente che scorre su tutto il ramo

R2-R1-R2; il suo modulo vale (v1-v2)/R1.

Sfortunatamente gli switch utilizzati per commutare le resistenze per il

guadagno sono caratterizzati da una certa capacitŕ parassita verso massa;

immaginate cosa succederebbe se i capi di R1 fossero collegati a

massa tramite due condensatori: se R1 fosse molto alta, una corrente

non trascurabile se ne andrebbe attraverso tali capacitŕ. Quindi la corrente

sulle R2 aumenterebbe, e con essa il guadagno. Questo fenomeno si

puň verificare in modo molto chiaro con PSPICE: facendo un'analisi AC si

evidenzia un picco alle alte frequenze.

Non mi viene in mente

nessun metodo efficace per compensare questo fenomeno in modo

"semplice", direttamente su ogni ramo della rete di commutazione del

guadagno e senza mettere dei condensatore in serie ad altri componenti (e quindi

tagliare le componenti DC, cosa che non vogliamo fare). Utilizzando invece un

amplificatore invertente, e ponendo la rete di commutazione al posto della

resistenza di retroazione, ci troviamo in questa situazione:

Ho giŕ riportato le due

capacitŕ parassite dovute agli switch analogici. Questo schema č spesso

utilizzato come esempio dei problemi "tipici" di cui puň soffrire un

amplificatore operazionale. :-)

Potete trovare molte informazioni sulla compensazione di questo tipo di circuito

in due interessanti documenti della National: AN-4

Monolitic Op Amp - The Universal Linear Component e AN-453

LH0024 and LH0032 High Speed Op Amp Applications. Senza scendere

troppo nei dettagli dico soltanto che le due capacitŕ riducono il margine di

fase del circuito alle alte frequenze, soprattutto per guadagni modesti (R2

piccola). Il circuito si avvicina molto all'instabilitŕ, come si puň vedere

simulandolo con PSPICE: nel caso dell'operazionale che ho usato, l'AD8057, c'č

un picco di risonanza (e quindi un aumento inaccettabile del guadagno) attorno

ai 10 MHz.

Per ovviare a questo problema č sufficiente inserire un condensatore in

parallelo a R2, introducendo uno zero nell'anello di retroazione e

compensando cosě il polo introdotto dall'operazionale e dalle capacitŕ

parassite. Questa per noi č una soluzione ideale, perché di immediata

applicazione; sarŕ sufficiente inserire un condensatore in parallelo a ogni

resistenza dello stadio di commutazione del guadagno, con valore calcolato

opportunamente in base alla resistenza.

Non so quanto vi

interessasse tutto ciň, ma per me (che sono relativamente nuovo al fantastico

mondo delle alte frequenze e delle capacitŕ parassite) č stato interessante

scoprirlo. Se qualcuno ha voglia di formalizzare queste considerazioni e

mostrare analiticamente la loro validitŕ, č il benvenuto: non č assolutamente

complicato, basta un modello di operazionale reale per piccoli segnali e qualche

formula. Io per ora passo la mano. ;-)

Dopo lo stadio

amplificatore/attenuatore c'č infine uno stadio sottrattore, che serve per

ripristinare la polaritŕ originaria del segnale (che era stata invertita dallo

stadio precedente) e per aggiungere l'offset di 2.5 V necessario per l'ingresso

dell'ADC.

Per l'implementazione di

questi stadi ho utilizzato l'AD8057 dell'Analog Devices, un operazionale

voltage-feedback ad alta velocitŕ e basso costo. Prendendo per buone le

simulazioni PSPICE che ho fatto sembra che il dispositivo si difenda piuttosto

bene fino a guadagni dell'ordine di dieci volte; dopodiché l'offset di tensione

in ingresso non trascurabile e il prodotto GBW non eccessivo iniziano a incidere

in modo rilevante sulle performance. Nella prossima sezione comunque riporterň

qualche grafico per dare un'idea piů precisa dell'entitŕ di questi problemi.

3. Stadio di

commutazione del guadagno. Questo stadio č il piů semplice, contiene

soltanto lo switch per la selezione AC/DC (pilotato da CTLOUT3) e la rete che

imposta la resistenza di retroazione dello stadio del guadagno descritto in

precedenza. La resistenza voluta č selezionata da un decoder, pilotato a sua

volta dai segnali CTLOUT0...2.

Vi sprono a esaminare gli

schemi e a considerarli con occhio critico.

Qualche grafico delle

prestazioni

Utilizzando il modello

PSPICE dell'AD8057, fornito direttamente da Analog Devices, ho fatto qualche

simulazione AC per verificare le prestazioni dello stadio di ingresso nel range

di frequenze che ci interessa (0...30 MHz). Le

analisi di

PSPICE vanno sempre prese col beneficio del dubbio; ci sono almeno un milione di

motivi per i quali la simulazione potrebbe discostarsi in modo considerevole

dalla realtŕ, non ultimo quello che i modelli forniti dai costruttori

descrivono soltanto le caratteristiche piů "importanti" dei dispositivi: spesso

sono utili per analisi molto specifiche, ma falliscono per analisi piů

complesse. In ogni caso i risultati sembrano piuttosto sensati e confermano

tutte le considerazioni fatte in precedenza.

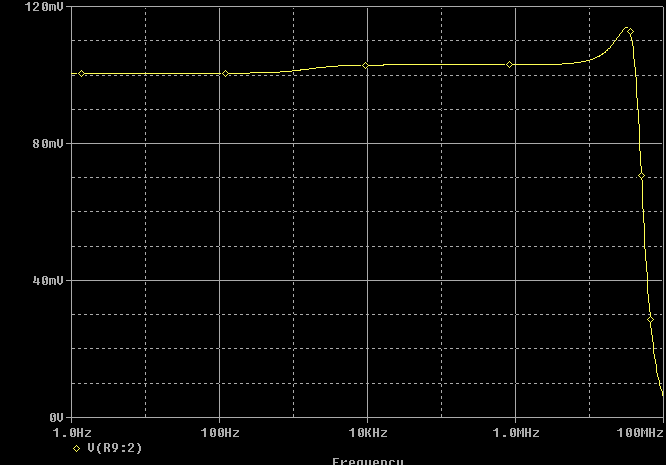

Questa ad esempio č

l'analisi AC nel caso che lo stadio di ingresso sia impostato a guadagno

unitario:

Si puň vedere il picco

di risonanza di cui ho parlato in precedenza. In questo caso non č nemmeno

cosě malvagio (permette di guadagnare qualcosina come banda passante) ma per

guadagni inferiori a uno diventa inaccettabile. Si noti anche il piccolo flesso

dalle parti di 1 kHz: esso č causato dalla non perfetta compensazione della

sonda in ingresso (ho utilizzato volutamente un valore leggermente sbagliato per

evidenziare il fenomeno e per enfatizzare l'importanza di questa taratura).

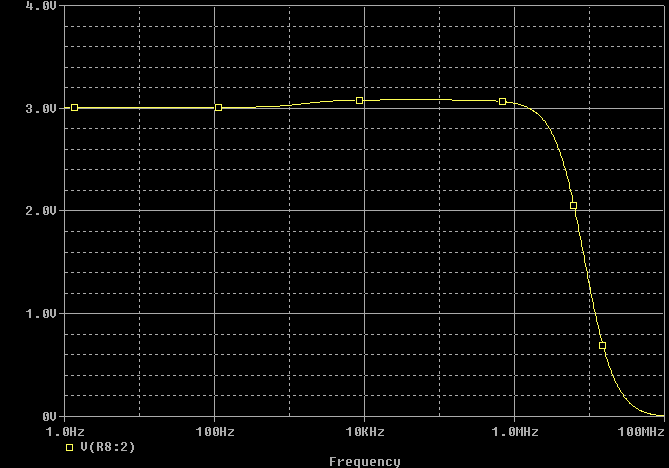

Questa č la stessa

analisi dopo che č stata inserita una capacitŕ in parallelo alla resistenza di

retroazione:

Il risultato ora č

soddisfacente. A 30 MHz il guadagno č ancora perfettamente unitario.

Questo invece č

l'estremo opposto, guadagno di trentadue volte:

Come si vede le

prestazioni sono peggiorate notevolmente. La banda č piatta fino a 2-3 MHz, poi

comincia il rovinoso crollo. A 30 MHz abbiamo ormai raggiunto un'attenuazione di

24 dB. Ho provato a fare qualche esperimento per migliorare la situazione (ad

esempio mettendo due amplificatori in cascata ognuno con un guadagno piů

basso), ma sono stati solamente palliativi. La realtŕ dei fatti č che il

dispositivo ha i suoi limiti, ci dobbiamo accontentare oppure spendere piů

soldi per un modello con prestazioni superiori. A titolo di esempio, usando lo

sfarzoso CLC425 della National (8.37 € da RS) abbiamo una risposta pressoché

piatta fino a un guadagno di 16 volte, e un'attenuazione di 4-5 dB per un

guadagno di 32 volte. Come sempre, tutto dipende da quanto si vuole spendere.

;-)

Indice

(precedente) Il firmware della CPLD

(prossimo) La

scheda madre

|